Процессоры Wafer Scale Engine достигли третьего поколения. Cerebras переходит на производство чипа, занимающего всю пластину, по техпроцессу 5 нм. Компания хочет сохранить энергопотребление и цену на прежнем уровне, но при этом сделать большой скачок в вычислительной производительности ИИ.

Процессоры Wafer Scale Engine достигли третьего поколения. Cerebras переходит на производство чипа, занимающего всю пластину, по техпроцессу 5 нм. Компания хочет сохранить энергопотребление и цену на прежнем уровне, но при этом сделать большой скачок в вычислительной производительности ИИ.

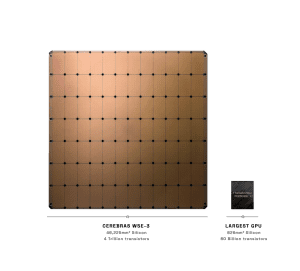

Летом 2019 года гигантский чип для вычислений искусственного интеллекта площадью 46.225 мм² привлек к себе немало внимания, так как представлял собой совершенно новую концепцию. Преемник был представлен в 2021 году. Уникальная особенность в том, что Cerebras не разрезает пластину на отдельные чипы, а оставляет 84 кристалла на пластине, соединяя их напрямую друг с другом.

Поэтому, хотя Cerebras и говорит о чипе площадью 46.225 мм². Здесь суммарная площадь для всех кристаллов, то есть ее нельзя напрямую сравнивать с самым большим GPU, доступным на данный момент. Тем не менее, сравнение все равно полезно: графический процессор GH100 от NVIDIA имеет 80 миллионов транзисторов на площади 814 мм².

WSE-3, предположительно, производится по техпроцессу 5 нм на заводах TSMC. Для WSE-3 также упоминается 84 независимых домена тактовых частот.

Собственно ядра ИИ (Sparse Linear Algebra Compute Cores) SLAC также претерпели некоторые изменения в третьем поколении микроархитектуры. Например, каждое из ядер CS-3 теперь имеет 8-Wide FP16 SIMD-блок – вдвое шире, чем у CS-2. Однако более подробной информации Cerebras не приводит.

| WSE-1 | WSE-2 | WSE-3 | |

| Техпроцесс | 16 нм | 7 нм | 5 нм |

| Площадь кристалла | 46.225 мм² | 46.225 мм² | 46.225 мм² |

| Число транзисторов | 1,2 трлн. | 2,6 трлн. | 4 трлн. |

| Ядра ИИ | 400.000 | 850.000 | 900.000 |

| SRAM | 18 Гбайт | 40 Гбайт | 44 Гбайт |

| Пропускная способность памяти | 9 PB/s | 20 PB/s | 21 PB/s |

| Пропускная способность интерконнекта | 100 PB/s | 220 PB/s | 214 PB/s |

Помимо производства по техпроцессу 5 нм, изменения WSE-3 выглядят не столь значительными. 850.000 ядер ИИ превратились в 900.000. Объем SRAM, распределенной по всем кристаллам, увеличивается с 40 до всего 44 ГБ. Пропускная способность памяти и пропускная способность внутреннего интерконнекта также существенно не изменились.

Тем не менее, количество транзисторов увеличилось с 2,6 до 4 триллионов. Следовательно, в микроархитектуре произошли более значительные изменения, чем можно предположить по количеству ядер ИИ или SRAM.

Мы уже обсуждали структуру сервера на WSE более подробно. Здесь также не должно быть особых изменений. Однако сейчас становится понятно, какая техническая инфраструктура необходима для того, чтобы такой «чип» вообще работал. Небольшой прирост SRAM может быть связан с тем, что к чипу можно подключать внешнюю память емкостью 1,5 ТБ, 12 ТБ и 1,2 ПБ. При этом пропускная способность памяти весьма велика, чтобы очень быстро передавать параметры больших языковых моделей LLM ядрам ИИ.

По данным Cerebras, WSE-3 может тренировать модели с 24 триллионами параметров. Текущие LLM, например, Llama2-70B, используют 70 миллиардов параметров.

Вместе с несколькими партнерами Cerebras объявила о разработке суперкомпьютеров для ИИ на WSE-3. Одним из них является Condor Galaxy 3, который должен быть запущен во втором квартале 2024 года. В Condor Galaxy 3 будут работать 64 системы CS-3. Теоретически можно создать кластеры до 2.048 систем CS-3.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).