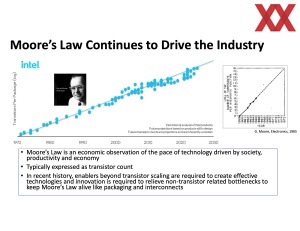

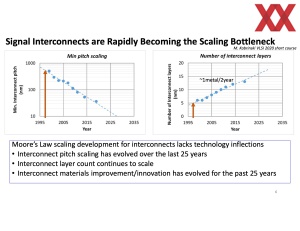

![]() На международной конференции IEEE International Electron Devices Meeting (IEDM 2023) полупроводниковые компании, исследовательские группы и университеты представили результаты своих последних исследований в области современных полупроводников. В этом году докладчики сосредоточились на развитии технологий подачи питания с обратной стороны кристалла Backside Power Delivery Networks (BSPDN), корпусировки и масштабирования транзисторов до 2 нм и менее. В этой новости мы сосредоточимся на разработках в области BSPDN.

На международной конференции IEEE International Electron Devices Meeting (IEDM 2023) полупроводниковые компании, исследовательские группы и университеты представили результаты своих последних исследований в области современных полупроводников. В этом году докладчики сосредоточились на развитии технологий подачи питания с обратной стороны кристалла Backside Power Delivery Networks (BSPDN), корпусировки и масштабирования транзисторов до 2 нм и менее. В этой новости мы сосредоточимся на разработках в области BSPDN.

Производители чипов, такие как Intel, TSMC, Samsung, а также исследовательские компании, такие как imec, приоткрывают на IEDM 2023 завесу тайны над новыми технологиями, которые мы увидим в полупроводниковом секторе в ближайшие годы или даже десятилетия. В случае с Intel результаты исследований представила группа Components Research (CR). Она занимается технологиями производства чипов и корпусировки. Когда, в какой форме и для какого продукта эти технологии будут использованы – совершенно другой вопрос.

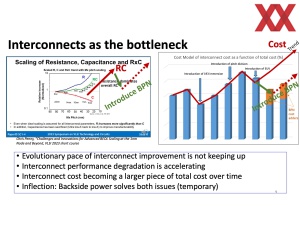

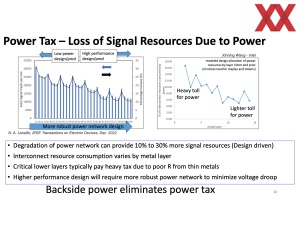

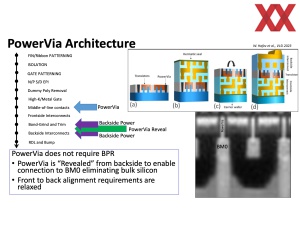

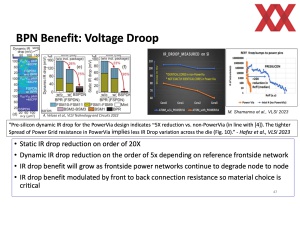

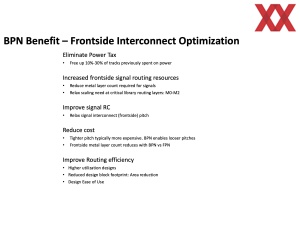

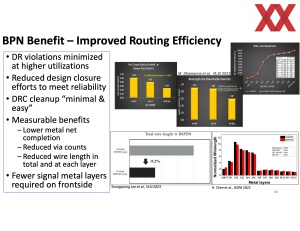

Но, конечно, иногда существует прямая связь между представленными технологиями и конкретными планами. В случае с PowerVia мы увидим подачу питания с задней стороны кристалла в первых процессорах, которые будут производиться по техпроцессу Intel 20A. Мы неоднократно подчеркивали преимущества линий PowerVia, когда питание и подача сигнала разделены. Например, в новости с VLSI в этом году, а также в публикации с первыми конкретными результатами, основанными на тестовом производстве Intel 4.

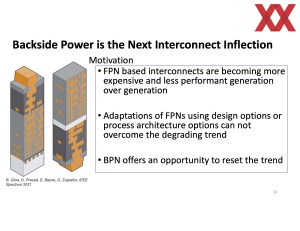

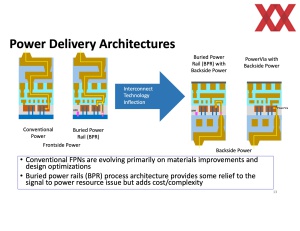

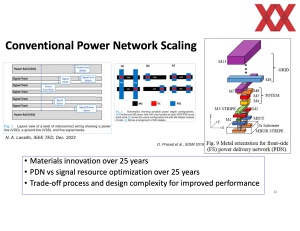

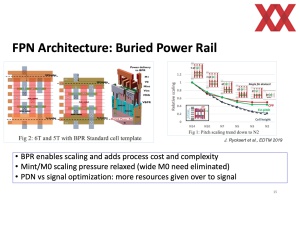

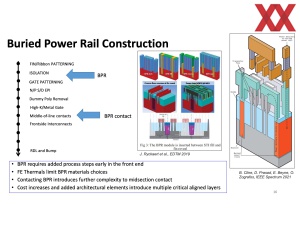

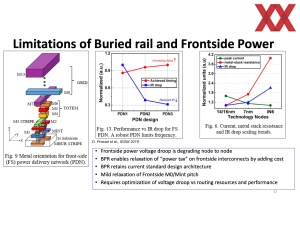

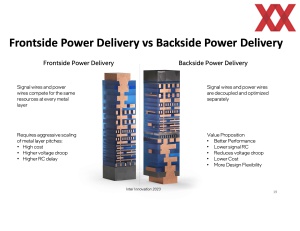

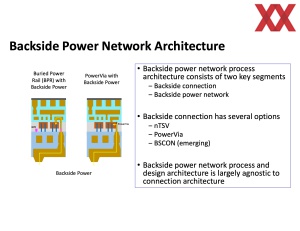

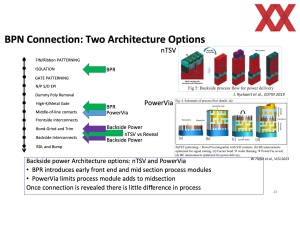

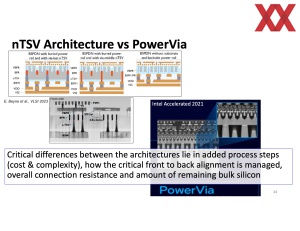

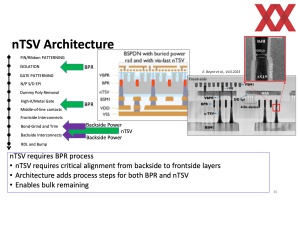

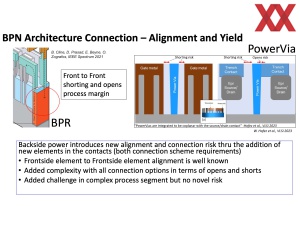

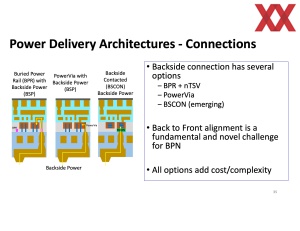

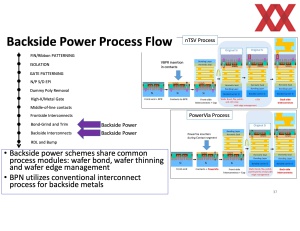

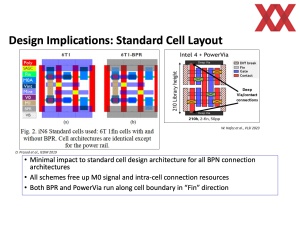

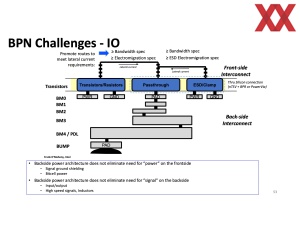

Однако технология PowerVia от Intel – лишь одна из многих разновидностей Backside Power Delivery Networks. Линии PowerVia подают питание с задней стороны кристалла непосредственно на транзисторную ячейку. Другая реализация - с помощью Buried Power Rails (BPR), которые интегрированы горизонтально в чипы и питают транзисторные ячейки. Однако линии BPR также могут быть реализованы с помощью фронтальной подачи питания (Frontside Power Delivery).

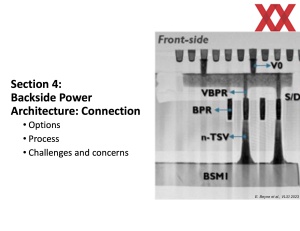

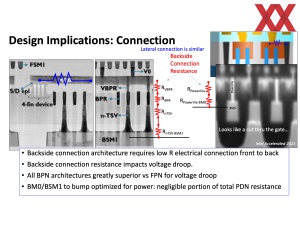

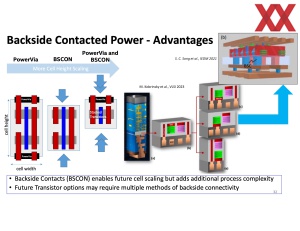

Но для следующих шагов в технологическом процессе и создания еще более тонких структур Intel придется выйти за рамки PowerVia. Для этого были разработаны контакты на задней стороне BackSide Contacts (BSCON). BSCON будут использоваться при укладке транзисторных ячеек в стек, что станет следующим шагом в транзисторной технологии. На данный момент Intel работает над RibbonFET, которые также известны как нанолистовые транзисторы. В первом поколении RibbonFET будут располагаться рядом друг с другом, но на следующем этапе они также будут укладываться друг на друга в стек, что позволит их эффективно масштабировать. Соответственно, необходимо разработать метод подачи на эти транзисторные ячейки необходимого напряжения. Именно здесь на помощь приходят контакты с обратной стороны кристалла.

Благодаря меньшей длине BSCON имеют меньшую емкость за пределами слоев распределения питания, что позволяет транзисторам переключаться быстрее и тем самым достигать более высокой тактовой частоты. С другой стороны, необходимо гарантировать стабильное напряжение питания, поэтому здесь было проведено большое количество исследований по разработке PowerVia и BSCON.

В будущих техпроцессах, где PowerVia еще не внедрены, они будут исключены, чтобы сэкономить место в вертикальной плоскости и увеличить плотность транзисторов. Что будет особенно важно для транзисторов Stacked RibbonFET (NMOS на PMOS и т.д.).

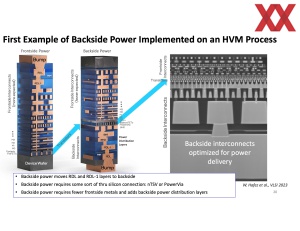

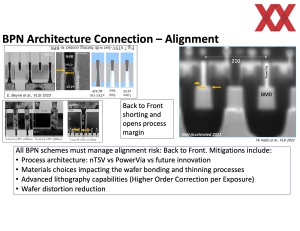

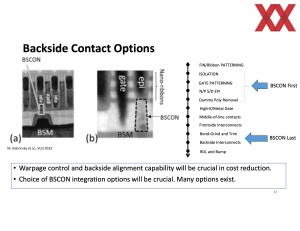

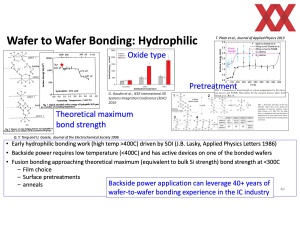

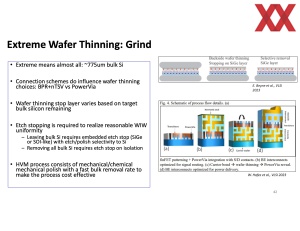

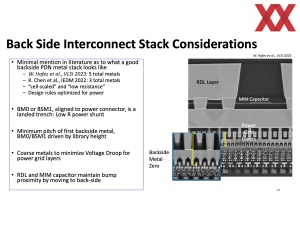

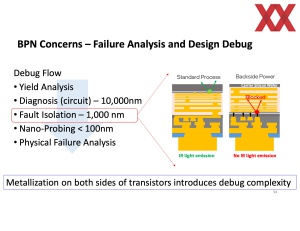

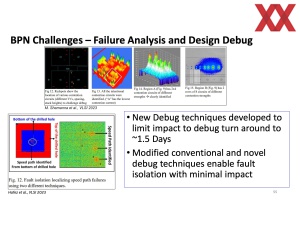

Чтобы подвести к транзисторам контакты с двух сторон (передача сигналов с одной стороны, питание с другой), пластины придется по-разному обрабатывать. Сначала экспонируется кристалл с металлическими слоями с передней стороны пластины, как это происходит в настоящее время. По мнению Intel, значительно менее сложный металлический слой M0 должен упростить процесс и здесь. Затем накладывается несущая пластина Carrier Wafer, обе пластины переворачиваются, задняя сторона экспонированной пластины спиливается до слоя транзисторов. Затем начинается установка Nano-TSV и металлических слоев питания.

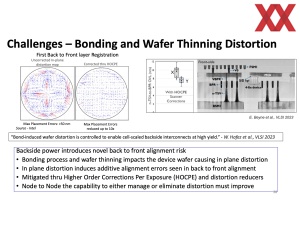

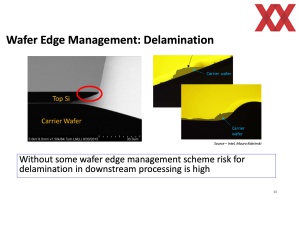

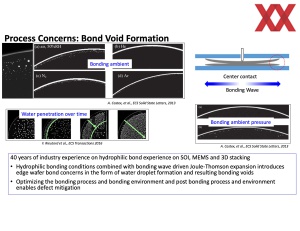

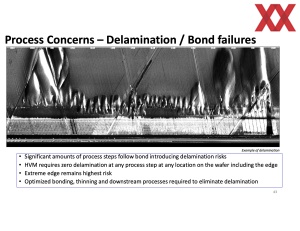

Однако процесс склеивания двух пластин и шлифовка негативно влияют и приводят к искажениям. Например, искажения в горизонтальной плоскости приводят к смещению BSPDN. Однако Intel работает над соответствующими технологиями, позволяющими минимизировать этот эффект.

В принципе, эта проблема знакома по корпусировке, когда все меньшие контактные площадки приходится соединять. Для Foveros Direct шаг Bump Pitch, то есть расстояние между контактами, уменьшиться до менее чем 10 мкм. TSMC использует собственные процессы корпусировки, такие как Hybrid Bonding, и шаг между контактами Bump Pitch составляет уже 9 мкм. TSV, используемые для PowerVia, в 500 раз меньше, чем TSV в современных корпусировках, что также подчеркивает необходимую точность процесса склеивания для BSPDN.

Можно ожидать появления PowerVia в следующем году вместе с процессорами Arrow Lake, выпускаемыми по техпроцессу Intel 20A, с которыми также будут использоваться RibbonFET. Но пройдет еще некоторое время, прежде чем мы увидим такие технологии, как BackSide Contacts (BSCON), в реальных продуктах.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).