С пятью ступенями техпроцесса за четыре года Intel планирует вернуть положение лидера. Современные настольные и серверные процессоры изготавливаются по техпроцессу Intel 7, а чипы Meteor Lake и Granite Rapids будут использовать технологию Intel 4, но Intel по-прежнему зависит от сторонних производителей чипов для многих кристаллов – в первую очередь, от TSMC. В середине десятилетия свою роль должно сыграть подразделение Intel Foundry Services, что совпадает с планами Intel по возвращению роли производителя чипов на передовых техпроцессах. Поэтому исследовательское подразделение Intel работает, не покладая рук, чтобы вывести компанию в лидеры.

С пятью ступенями техпроцесса за четыре года Intel планирует вернуть положение лидера. Современные настольные и серверные процессоры изготавливаются по техпроцессу Intel 7, а чипы Meteor Lake и Granite Rapids будут использовать технологию Intel 4, но Intel по-прежнему зависит от сторонних производителей чипов для многих кристаллов – в первую очередь, от TSMC. В середине десятилетия свою роль должно сыграть подразделение Intel Foundry Services, что совпадает с планами Intel по возвращению роли производителя чипов на передовых техпроцессах. Поэтому исследовательское подразделение Intel работает, не покладая рук, чтобы вывести компанию в лидеры.

Одна из составляющий успеха – сквозные линии PowerVia, которые Intel использует для подачи питания с задней стороны чипа. Сигнальные пути и линии подачи питания будут отделены друг от друга, что дает различные улучшения. Вместе с технологией транзисторов RibbonFET, PowerVia будет использоваться для производства первых чипов Intel 20A и Intel 18A с 2024 года. На конференции VLSI Symposium Intel говорила о том, что PowerVia изначально планировалось использовать для Intel 4.

Но во время анонса расширения производственных мощностей в Орегоне (D1X Mod 3) Intel явно дала понять, что PowerVia и RibbonFET будут использоваться, начиная с техпроцесса Intel 20A. А до того времени Intel продолжит использовать техпроцессы Intel 4 и Intel 3 в нынешнем виде. Сейчас проходит внутренняя процедура тестирования, которую Intel детально не раскрывает, но в финальных продуктах тестовый техпроцесс не будет задействован.

По презентации с конференции VLSI понятно, что Intel добавила внутренний тестовый техпроцесс, чтобы минимизировать риски при переходе на Intel 20A.

Разные способы подачи питания с задней стороны чипа

Но сначала позвольте объяснить, почему не только Intel сегодня работает над данной технологией, известной как Backside Power Delivery Network (BS-PDN).

Современные техпроцессы предусматривают линии питания и данных с одной стороны. Здесь располагаются как интерконнекты, так и слои чипа. Причем сегодня может быть до 14 слоев, исследователям приходится прилагать все больше усилий к поиску материалов, которые смогут обеспечить как эффективное питание, так и целостность передачи сигналов. Все это увеличивает затраты, при этом технические ограничения никуда не деваются, приходится бороться с падением напряжений и помехами при передаче сигналов.

Подача питания с задней стороны чипа разделяет линии питания и передачи сигналов. С лицевой стороны чипа по-прежнему располагаются проводники передачи данных, а проводники Via и слои подачи питания подходят с задней стороны. К преимуществам новой технологии можно отнести потенциально более высокую производительность и меньшие затраты. Но есть и крупный недостаток – производство придется переделывать, что скажется на доле выхода годных кристаллов и надежности, необходимо решать проблему отведения тепла и т.д. Intel как раз исследует данные проблемы через внутренние тесты техпроцессов на основе Intel 4 и Intel 20A, пытаясь найти решения.

Но не все в реализациях BS-PDN так просто. Часто речь идет просто о Buried Power Rails – сзади транзисторов оставлены дорожки питания, но непосредственно питание по-прежнему подается с лицевой стороны чипа. Поэтому здесь имеются все те же недостатки по тесно расположенным линиям питания и передачи данных.

Buried Power Rails с BS-PDN – следующий шаг, питание уже подается с задней стороны чипа, поэтому линии питания и данных разделены. Но лицевая сторона чипа все равно используется для подачи питания на самом нижнем уровне (M0).

Что касается технологии Intel PowerVia, здесь используются сквозные проводники nano-TSV, которые напрямую подключены к транзисторам.

Intel планирует минимизировать риски производства. Поэтому компания применяет отдельные шаги в виде модулей, после чего объединяет их. Например, для внутреннего рискового производства 20А сначала реализован модуль FinFET. Затем тестируется модуль PowerVia с nano-TSV и BS-PDN. Параллельно ведется разработка транзисторов RibbonFET, которые вместе с Nano-TSV будут использоваться в техпроцессе Intel 20A – и технологии PowerVia будут финализированы.

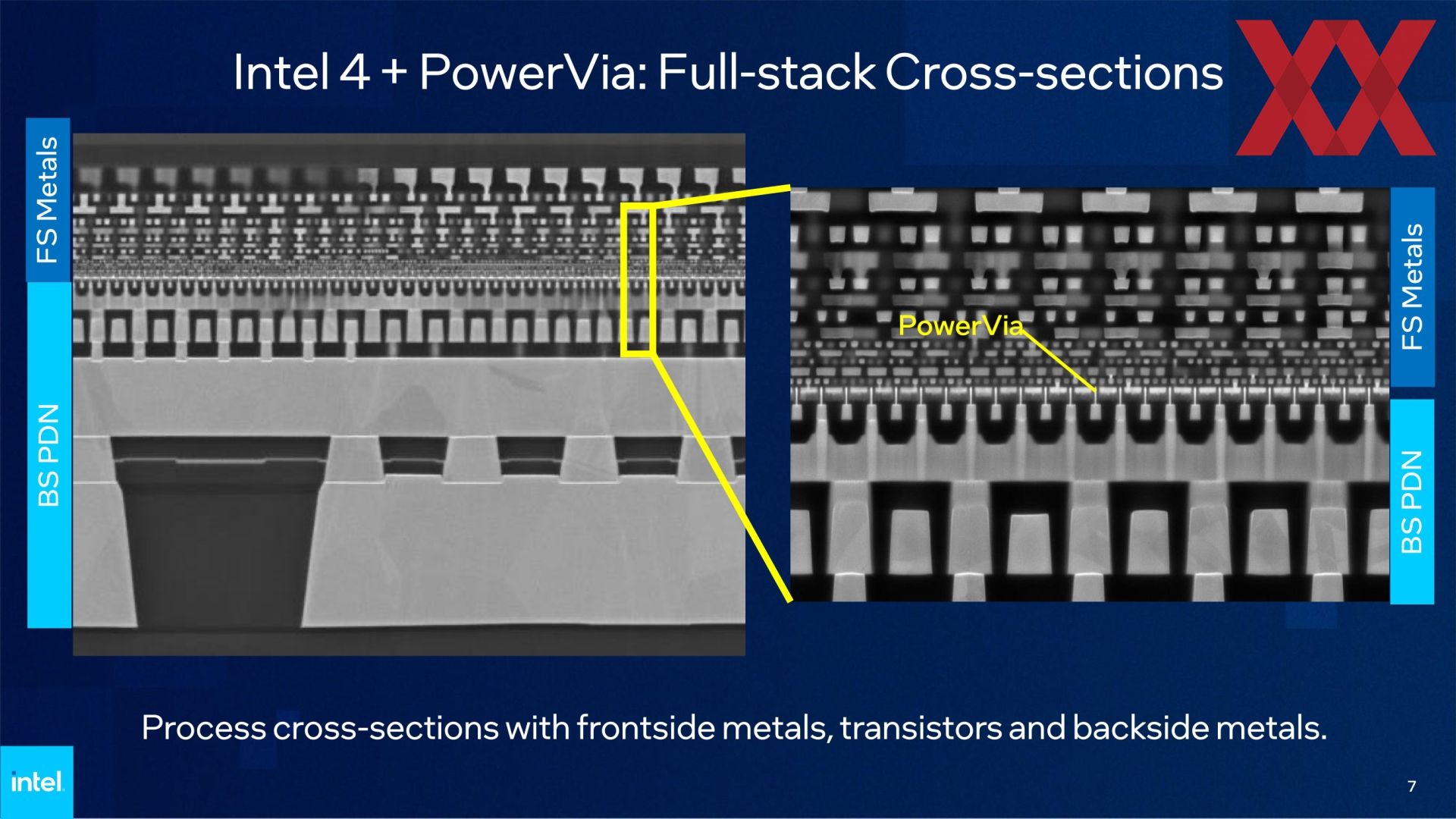

На срезе тестового чипа Intel 4 можно видеть металлические слои с лицевой стороны и BS-PDN с задней стороны. Крупные слои и сквозные проводники PS-PDN позволяют эффективно подводить питание к транзисторам, а металлические слои с лицевой стороны сравнительно упрощаются, их можно располагать ближе друг к другу. Белые колонны, на которые указывает обозначение PowerVia – это nano-TSV.

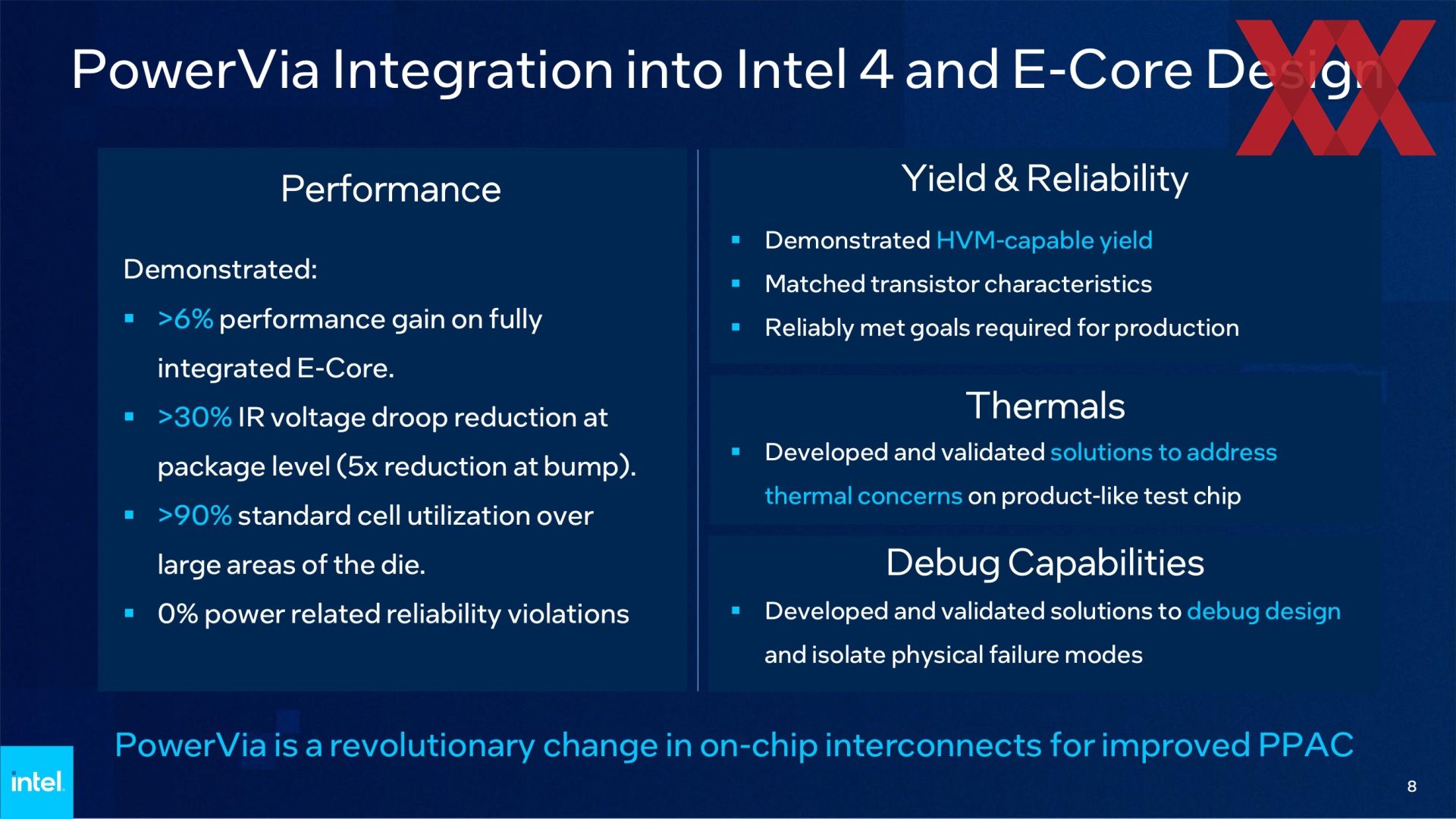

В рамках тестирования Intel смогла выпустить эффективные ядра по техпроцессу Intel 4 с PowerVia, после чего сравнила его с E-ядром Intel 4 без нового питания. Данное E-ядро предназначается для процессоров Meteor Lake. Производительность E-ядра удалось увеличить на 6%. Падение напряжений удалось снизить на 30%, при этом Intel может использовать более 90% площади чипа для стандартных ячеек.

Приведем некоторые спецификации чипа:

- 22 млн. транзисторов для e-ядра

- Одно E-ядро на квадрант

- Каждое E-core имеет площадь 2,9 мм²

- Второй чип с 40% Design of Experiment (DOE)

- Кристалл имеет площадь 4 x 8,3 = 33,2 мм²

- Частота 3 ГГц

- Рабочее напряжение 1,1 В

С другой стороны Intel подтверждает, что производство по техпроцессу Intel 4 с PowerVia уже достигло доли выхода годных кристаллов, подходящей для массового производства. То есть при производстве не было обнаружено серьезных проблем, несмотря на то, что с обратной стороны подложка спиливалась до уровня транзисторов.

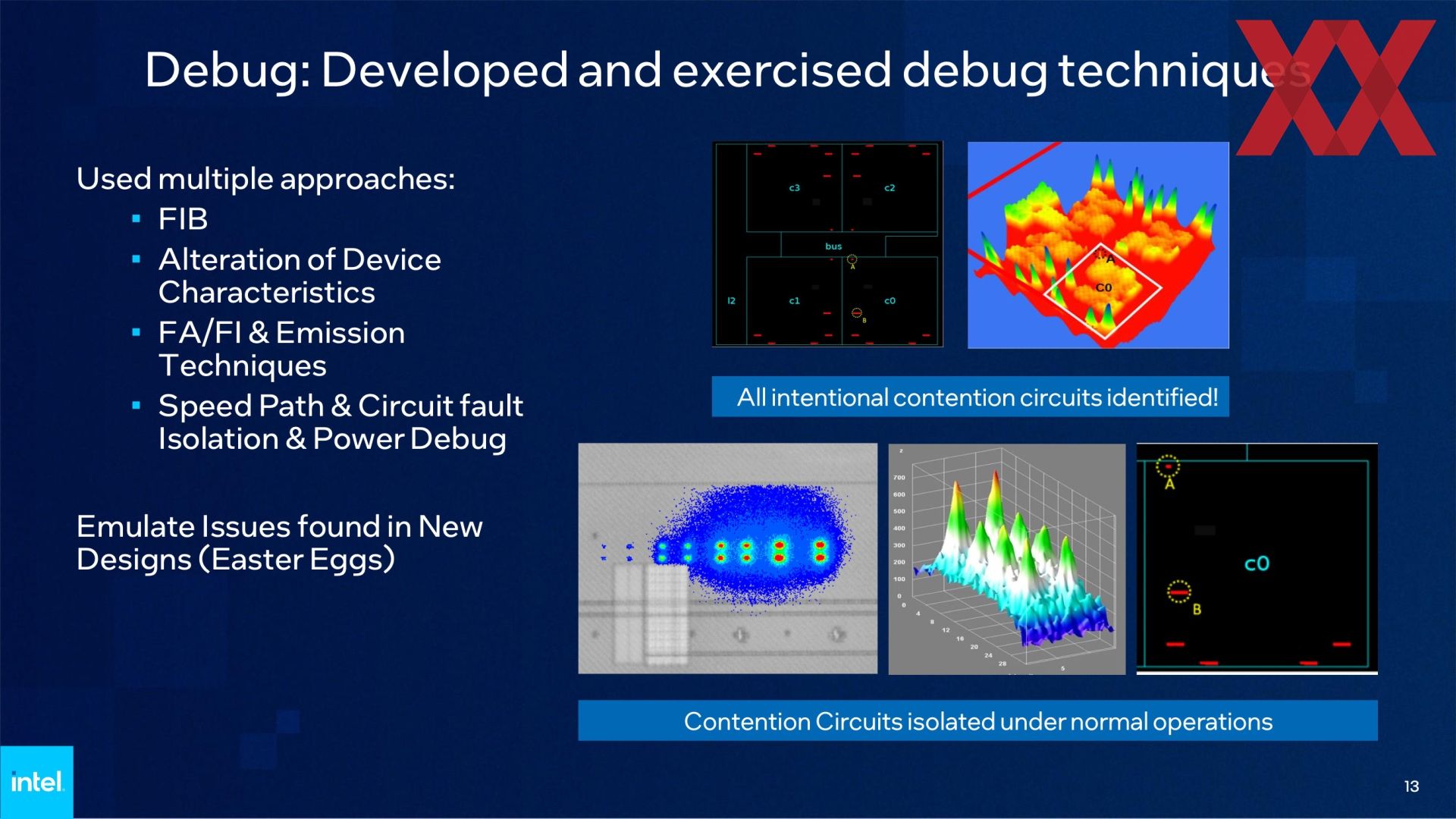

Что касается охлаждения, то здесь помогает сторона чипа, которая ранее не использовалась для этого. Производители кристаллов, такие как AMD и Intel, указывают оптимальную толщину кристалла, причем он не должен быть слишком тонким, так как тепло распространяется во всех направлениях. Мы уже опубликовали заметку по данному вопросу чуть раньше. Добавление BS-PDN гарантирует определенный уровень отведения тепла. Но обратная сторона чипа весьма важна для отладки, чтобы Intel смогла находить ошибки в дизайне и исправлять их. Мы опубликовали статью и по этому вопросу, где рассказали о посещении завода по производству полупроводников в Израиле, а также лаборатории Debug & Development Labs. Так что Intel пришлось найти какие-то решения, чтобы выполнять отладку чипа.

Пока все выглядит хорошо

Анализ техпроцесса Intel 4 с PowerVia дает убедительные результаты. Подробности Intel представит на VLSI Symposium.

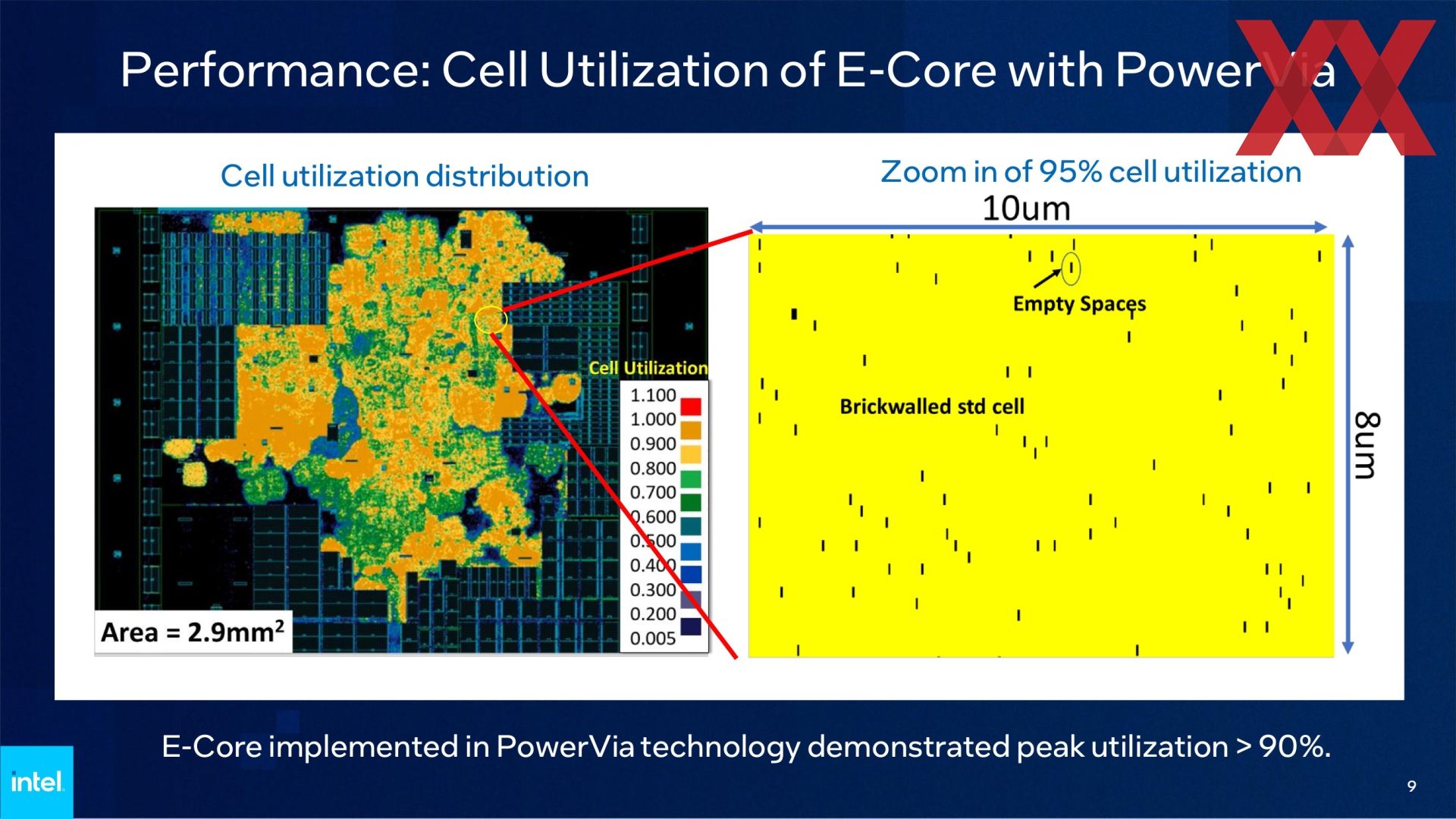

На диаграмме выше показано использование стандартных ячеек для e-ядра. На значительной площади процент составляет 80-90%, но есть и меньшие уровни, что вполне ожидаемо. Подобная картина вырисовывается при дизайне любых ядер, но чем плотнее удается размещать транзисторы, тем лучше. Большие темные области могут быть кэшами, их сложно уплотнять даже у современных процессоров.

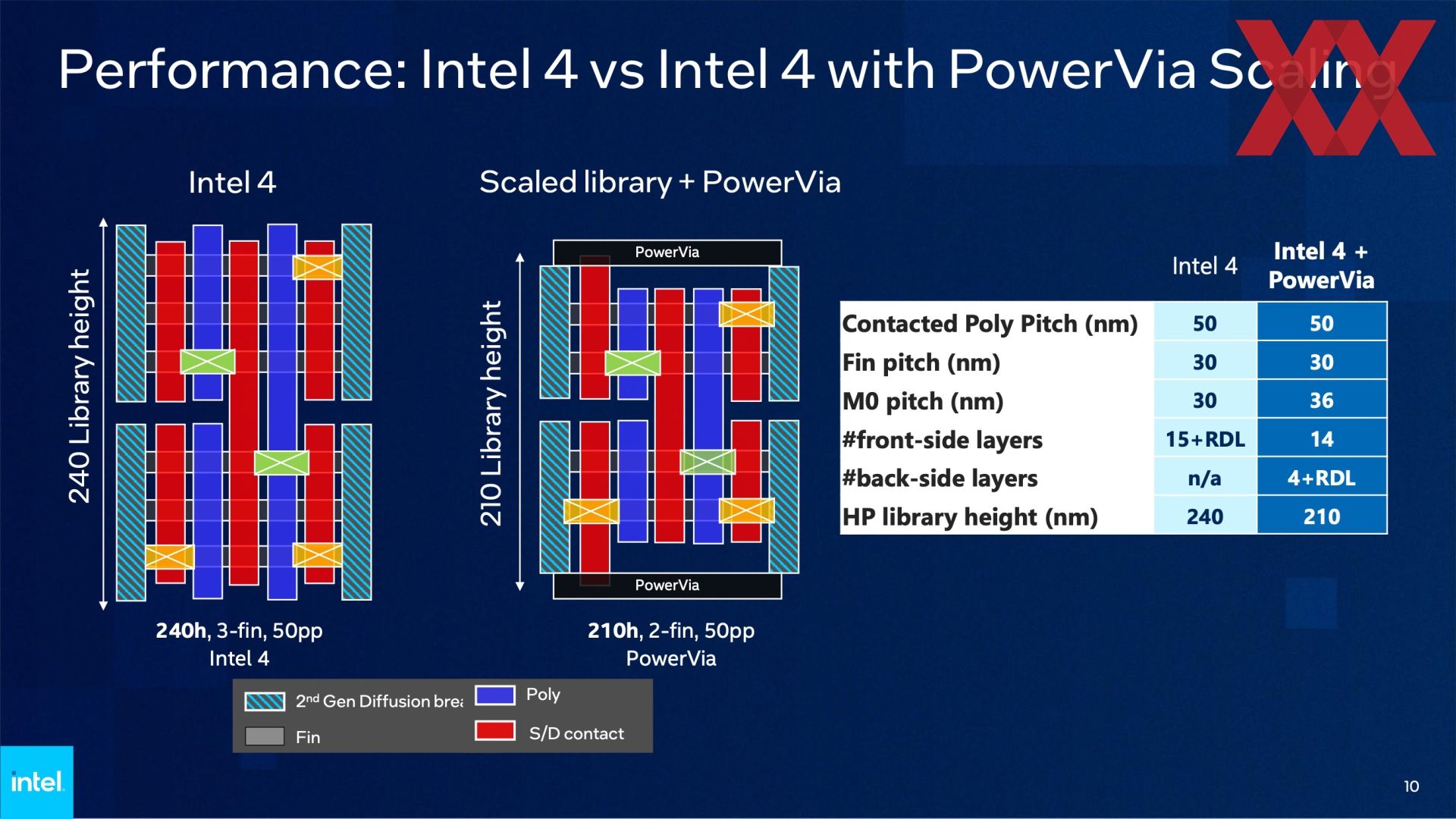

Библиотека ячеек Intel 4 опирается на дизайн 3+3: три ребра снизу, три сверху, общая толщина составляет 240 нм. В случае Intel 4 + PowerVia используется дизайн 2+2. Контакты PowerVia расположены сверху и снизу каждой ячейки, толщина – 210 нм. Более тонкий дизайн позволил Intel уменьшить размер ячеек, но при этом производительность осталась на высоком уровне.

Сравнение металлических слоев показывает, что Intel увеличила шаг у нижнего слоя M0 c 30 до 36 нм. Число слоев с лицевой стороны чипа уменьшилось, но были добавлены слои BS-PDN сзади. Впрочем, уменьшение сложности слоя M0 все это с лихвой компенсирует.

По сравнению с Intel 4, техпроцесс Intel 4 с PowerVia на два квартала обгоняет нынешний техпроцесс для Meteor Lake по плотности дефектов. То есть интеграцию PowerVia не стали делать всеми силами, и она не стала препятствием. Intel не указывает значения по оси Y, поэтому приходится оперировать относительной плотностью дефектов. Но Intel считает, что PowerVia уже готова к массовому производству.

Intel на тестовом чипе установила четыре e-ядра. Причем у каждого были разные характеристики, были даже специально добавленные ошибки, чтобы можно было протестировать отладку.

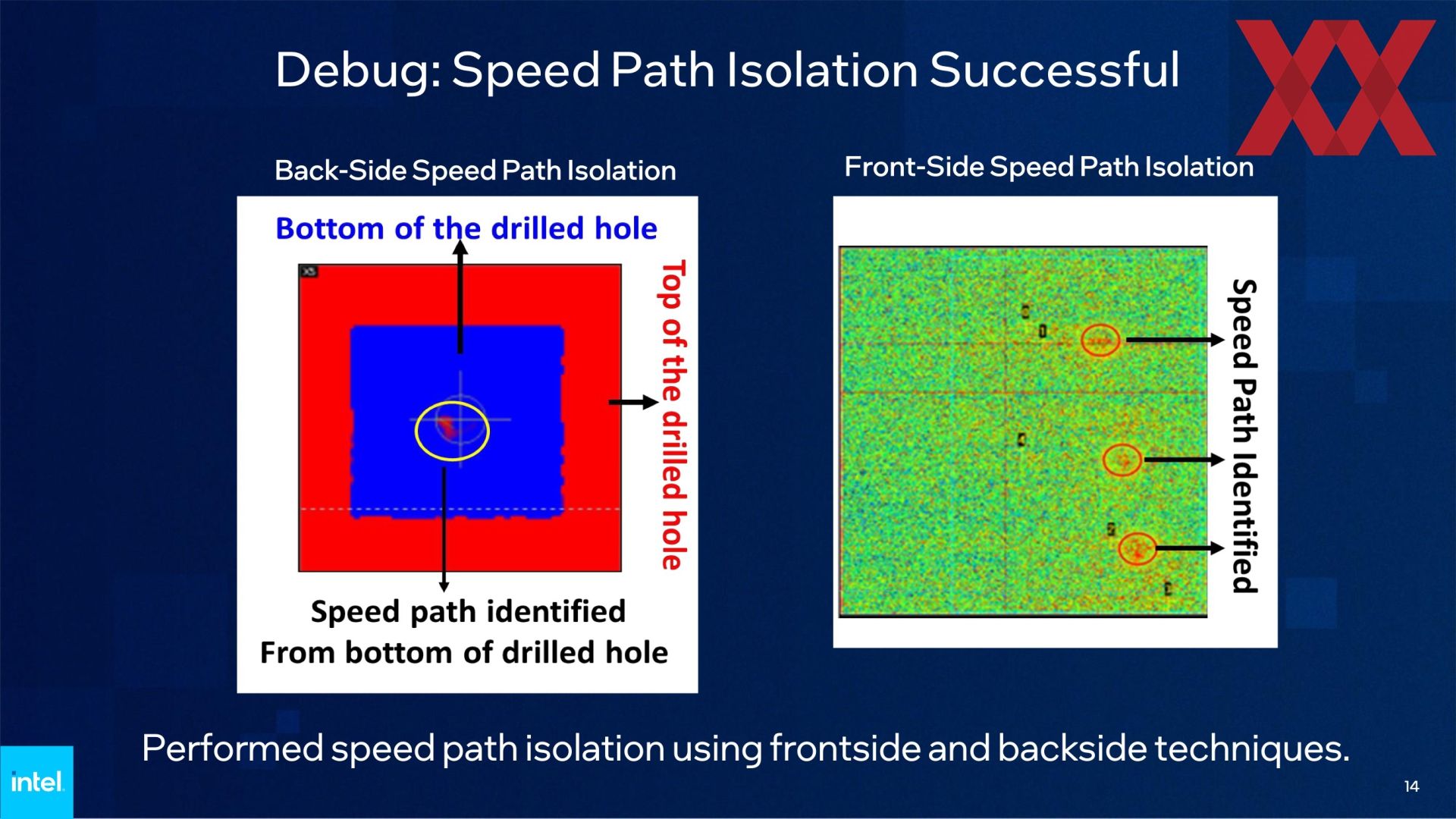

Ошибки были тщательно определены и проанализированы. При отладке используются физические средства, такие как сверление отверстий с помощью сфокусированного ионного луча FIB (Focused Ion Beam) с обеих сторон, и здесь Intel тоже не видит каких-либо препятствий для массового использования PowerVia.

Intel не видит препятствий и по охлаждению, поскольку температурные характеристики остаются в ожидаемых диапазонах в зависимости от энергопотребления и после добавления PowerVia. Для тестирования 30% чипа было использовано под структуры, которые просто выделяют максимальное количества тепла.

Сложность меняется

Как можно видеть, компромисс Intel был в менее сложном металлическом слое M0 и дополнительных четырех слоев проводников PowerVia. По информации Intel, на разработку слоя M0 уходило настолько много усилий, что добавление четырех менее сложных слоев сзади кристалла с лихвой компенсируется упрощением M0.

Также упрощаются и инструменты EDA (Electronic Design Automation), которым необходимо создавать дизайн лицевой стороны, имеющей до 14 слоев.

Меняется и работа с подложками в чистой комнате. Сначала экспонируются металлические слои чипа с лицевой стороны, как и раньше. Как указывает Intel, существенно менее сложный металлический слой M0 сказывается и здесь.

Затем добавляется несущая подложка, после чего две подложки переворачиваются, и задняя сторона экспонированной ранее подложки спиливается до уровня транзисторов. Затем добавляются сквозные проводники nano-TSV и металлические слои питания.

PowerVia с 2024 года

Intel уверена, что технология PowerVia будет полностью готова в 2024 году вместе с техпроцессом Intel 20A. Помимо процессоров, Intel сможет улучшить техпроцесс для производства GPU и ускорителей ИИ, которые смогут дать более высокую производительность и лучшую эффективность.

Intel с технологией PowerVia и ленточными транзисторами RibbonFET пытается вернуться на передовую разработки полупроводников. Судя по имеющейся информации от конкурентов, Intel находится на один шаг впереди – если представит Intel 20A в 2024 году. Конечно, Intel желает получить преимущество, в первую очередь, для своих продуктов. Но Intel будет предлагать свое производство и внешним клиентам.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).