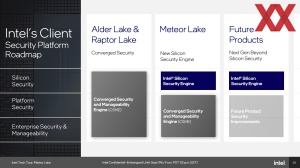

Процессоры Meteor Lake для будущих ноутбуков предвещают новую эру в дизайне потребительских CPU Intel. Сначала Intel перешла на дизайн тайлов с процессорами Xeon, теперь настала очередь клиентского сегмента. В конечном итоге мы получим аналог «системы на чипе» (SoC) с несколькими кристаллами в одной корпусировке. Intel работает над Meteor Lake уже четыре года, но некоторые базовые компоненты были доступны гораздо раньше. В статье мы рассмотрим (почти) все подробности процессоров Meteor Lake.

Процессоры Meteor Lake для будущих ноутбуков предвещают новую эру в дизайне потребительских CPU Intel. Сначала Intel перешла на дизайн тайлов с процессорами Xeon, теперь настала очередь клиентского сегмента. В конечном итоге мы получим аналог «системы на чипе» (SoC) с несколькими кристаллами в одной корпусировке. Intel работает над Meteor Lake уже четыре года, но некоторые базовые компоненты были доступны гораздо раньше. В статье мы рассмотрим (почти) все подробности процессоров Meteor Lake.

Процессоры Meteor Lake официально на рынок еще не вышли. Но на сегодняшний день мы уже можем говорить о технических аспектах, хотя пока нет ни списка моделей, ни подробностей номенклатуры. Поэтому сегодня мы можем раскрыть, в лучшем случае, максимальные конфигурации. Тактовые частоты и уровни Power Limit будут объявлены Intel несколько позднее.

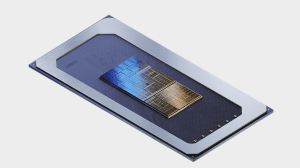

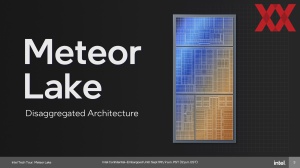

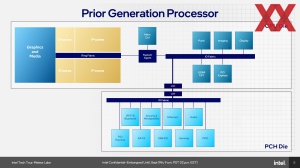

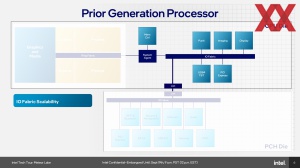

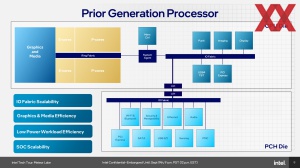

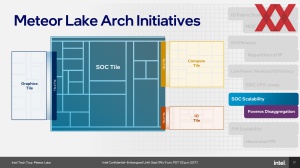

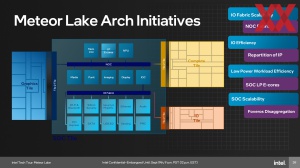

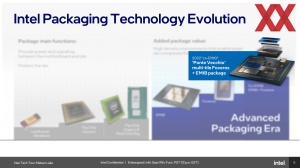

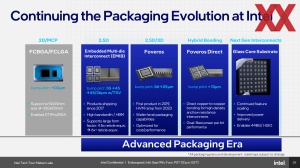

С течением времени в процессор интегрировалось все больше и больше компонентов: более одного ядра, контроллер памяти, блок интегрированной графики и, наконец, все больше функций ввода/вывода, которые раньше были реализованы через южный и северный мосты. Теперь мы развернулись в обратном направлении и встали на путь дезинтеграции, если можно так сказать. Для большей гибкости производства и, в конечном счете, расширения ассортимента процессор снова разбивается на компоненты, которые разрабатываются и производятся отдельно друг от друга и, наконец, снова собираются вместе.

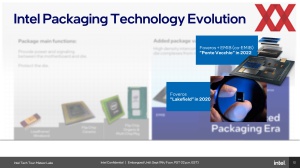

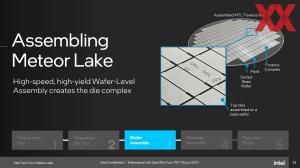

Немаловажным фактором является производство, особенно корпусировка, которая до сих пор часто была сравнительно простой с технической точки зрения. Но сегодня она все чаще оказывается в центре внимания. Недавно во время посещения площадки Intel в Малайзии мы смогли воочию убедиться в том, насколько важна корпусировка уже сейчас и насколько она будет важна в будущем.

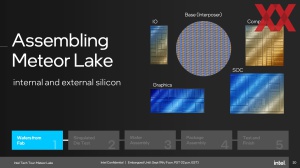

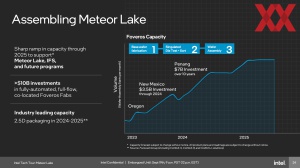

Там мы уже могли видеть, как собираются первые процессоры Meteor Lake. Отдельные чипы поступают из Ирландии и Тайваня, проходят в Орегоне передовую корпусировку (для массового производства будут задействованы мощности в штате Нью-Мексико), а затем поступают в Малайзию для окончательной корпусировки.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).

Дезинтегрированный дизайн и составные элементы

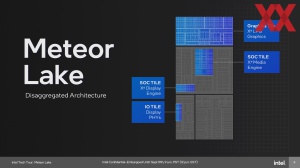

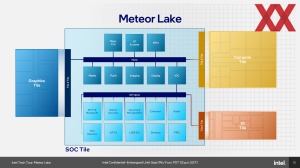

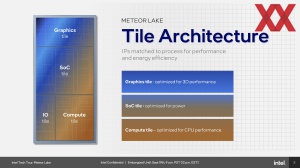

Процессор Meteor Lake состоит из пяти отдельных кристаллов, которые соединены между собой Foveros:

- Compute Tile (с ядрами CPU): Intel 4

- Графический тайл: TSMC N5

- SoC-тайл: TSMC N6

- Тайл ввода/вывода: TSMC N6

- Базовый тайл: Intel 22FFL

С первого взгляда видно, что Intel производит только вычислительный и базовый тайлы. Все остальное поставляется TSMC. Intel решила, что для текущей версии Meteor Lake часть тайлов лучше производить на мощностях TSMC. Мотивы просты: TSMC обладает необходимыми мощностями и может, например, изготовить графический тайл с идеальными характеристиками - тактовой частотой, энергопотреблением и площадью кристалла. В определенной степени это относится к тайлам SoC и ввода/вывода.

Compute Tile содержит вычислительные ядра, но впервые Intel использует E-ядра и в других тайлах - подробнее об этом позже. E-ядра Meteor Lake основаны на дизайне Crestmont. Ядра P – на дизайне Redwood Cove. Intel может менять вычислительные тайлы, то есть предлагать их в разных конфигурациях. Пока что с уверенностью можно утверждать только появление конфигурации 6P+8E.

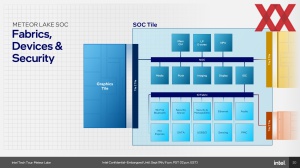

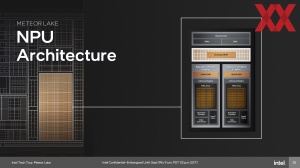

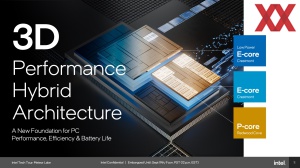

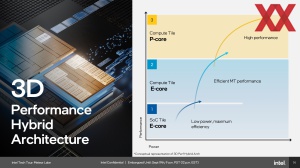

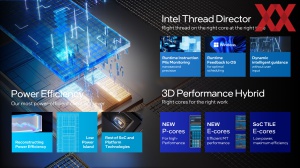

В состав SoC-тайла входят LP E-ядра. То есть P- и E-ядра в вычислительном тайле дополняются LP E-ядрами в тайле SoC, что Intel называет 3D Performance Hybrid Architecture. Кроме того, в SoC-тайле имеется движок искусственного интеллекта NPU AI, модуль WiFi 7 и Bluetooth, медиаблок для AV1 и 8K HDR с возможностью вывода сигналов дисплея через HDMI 2.1 и DisplayPort 2.1, а также контроллер памяти.

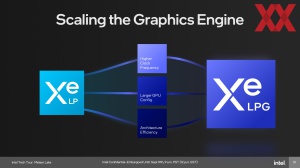

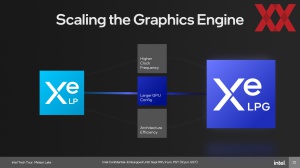

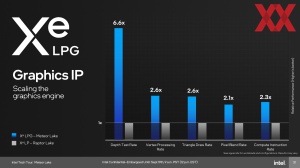

Графический тайл использует архитектуру Xe-LPG, на деталях которой мы остановимся чуть ниже. Предполагается, что соотношение производительности на ватт будет в два раза лучше, чем у Xe-LP, то есть предыдущего блока интегрированной графики. Графический тайл будет выпускаться в двух вариантах расширения.

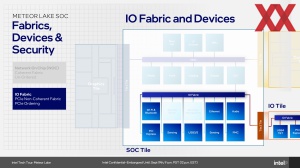

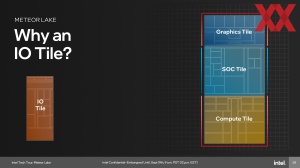

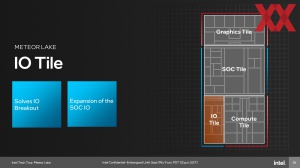

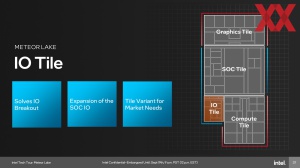

I/O Tile отвечает за такие функции, как Thunderbolt и PCI Express. I/O Tile тоже выйдет в двух версиях, которые будут предоставлять большее и меньшее количество линий PCI Express в зависимости от требований по вводу/выводу.

Однако дезинтеграция имеет преимущества не только с точки зрения производства кристаллов. Есть польза и с точки зрения отдельных функций. Intel может подобрать такое сочетание функций, которое оптимально подходит для целевых сценариев использования.

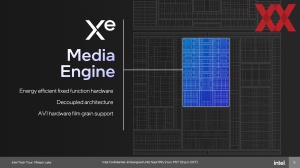

До сих пор медиаблок был компонентом интегрированного графического процессора. Для декодирования видео всегда требовалось разбудить и задействовать Core Complex, включая кэши и интерконнект. Но Core Complex и вычислительные ядра с кэшами не имели никакого отношения к декодированию, питание на них подавалось совершенно напрасно, что увеличивало энергопотребление.

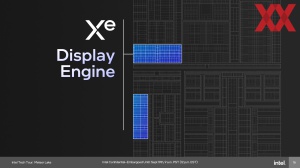

Теперь медиаблок перешел в состав SoC-тайла, поскольку он выполняет важные функции для многих областей применения. Core Complex находится в вычислительном тайле, а графический тайл теперь содержит только потоковые процессоры для рендеринга (и блоки AMX для некоторых приложений искусственного интеллекта). Движок дисплея также располагается в тайле SoC, так что для визуального вывода информации не нужно использовать дополнительные блоки или тайлы. На этом этапе становится ясно, что благодаря отделению медиаблока для декодирования видеоматериала нужен только тайл SoC. А вычислительный и графический тайл для этого уже не нужны.

В тайле SoC используются ядра LP E. Они также основаны на дизайне Crestmont. Здесь установлены максимум два ядра, которые совместно используют 4 Мбайт кэш-памяти L3. Эти E-ядра работают в другом окне по кривой «тактовая частота/напряжение». Кроме того, тайл SoC производится компанией TSMC по техпроцессу N6, а остальные ядра E и P в вычислительном тайле Intel – по Intel 4. В связи с этим различаются рекомендации и характеристики при проектировании транзисторов.

Архитектура P- и E-ядер

Производительные ядра (Redwood Cove)

Как уже отмечалось, ядра P базируются на дизайне Redwood Cove. Однако изменения по сравнению с предшественником Golden Cove не особенно велики. Точнее говоря, предполагается, что производительность IPC будет практически идентична Golden Cove, так что в Meteor Lake можно добиться увеличения одноядерной производительности только за счет более высокой тактовой частоты, а увеличения многопоточной производительности – за счет большего количества ядер.

Очевидно, что при разработке Redwood Cove в составе Meteor Lake основное внимание уделялось эффективности. Но ядра Redwood Cove будут использоваться и в других процессорах, и здесь прирост IPC, безусловно, имел бы смысл.

Каждое P-ядро имеет в своем распоряжении 46 кбайт кэша данных и 64 кбайт кэша инструкций L1, а также 2 Мбайт собственного кэша L2.

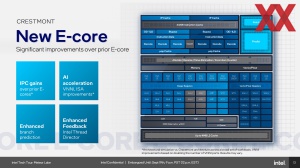

Эффективные ядра (Crestmont)

По сравнению с предшествующей архитектурой Gracemont ядра Crestmont в Meteor Lake, как утверждается, получили прирост производительности IPC на 4%. Каждое ядро имеет в своем распоряжении 32 кбайт кэша данных и 64 кбайт кэша инструкций L1. Объем кэш-памяти L2 составляет 4 Мбайт на четыре ядра E - как и в текущих моделях Raptor Lake.

Более подробно о новых архитектурах P- и E-ядер мы расскажем на презентации новых процессоров. На данный момент мы можем поделиться только информацией о довольно скромном росте IPC.

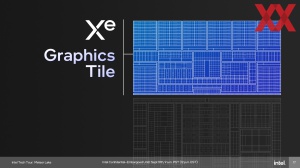

Графический тайл с Xe-LPG

Наряду с вычислительным тайлом важное значение имеет тайл интегрированной графики. Как уже говорилось, графический блок процессоров Meteor Lake должен иметь в два раза более высокое соотношение производительности на ватт по сравнению с предшественником.

Как мы отмечали выше, движки медиа и дисплеев, а также собственно графические блоки теперь не располагаются в одном месте чипа и не собраны полностью в одном тайле, а распределены таким образом, чтобы их можно было использовать максимально эффективно. Потоковые процессоры, включая кэш, находятся в графическом тайле. Медиа-движок расположен в тайле SoC, как и движок дисплея. Тайл ввода/вывода содержит интерфейсы и PHY для видеовыходов.

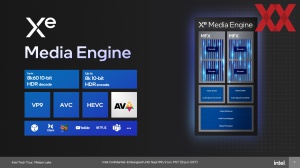

Поддерживаются такие распространенные форматы видео и изображений, как JPEG, MPEG, AV1, VP9 и HEVC. Причем декодирование и кодирование поддерживаются в форматах вплоть до 8K@60 в 10-битном разрешении. Медиадвижок содержит два MFX-движка, в каждом из которых есть декодер и кодер. Все функциональные блоки – с фиксированным набором функций, что должно обеспечивать высокую производительность и эффективность. Такого подхода придерживаются все производители чипов, встраивающие в свои процессоры специализированные кодеры и декодеры.

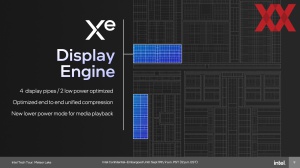

Движок дисплеев может управлять четырьмя дисплеями. С двумя видеовыходами движок дисплеев работает в идеальном окне эффективности. Поддерживаются стандарты HDMI 2.1 и DisplayPort 2.1 – один дисплей 8K@60 или четыре 4K@60.

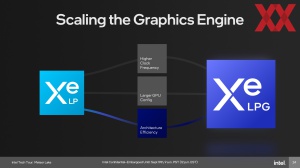

Для графического тайла используется архитектура Xe-LPG. По сути, она основана на первой архитектуре Xe (Arc / Xe-HPG), но была оптимизирована под мобильную работу. В том числе и благодаря производству на мощностях TSMC по технологии N5.

В результате на графическом тайле можно одновременно выставить низкое напряжение и высокие тактовые частоты. Чипы Arc, которые производятся по техпроцессу N6 на TSMC для настольных видеокарт, работают с другим окном эффективности и кривой напряжение/частота, чем графический тайл Meteor Lake.

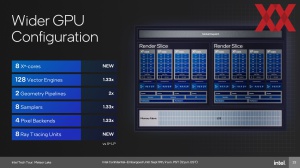

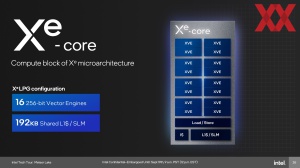

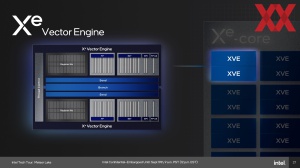

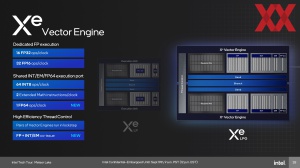

В максимальной конфигурации тайл содержит восемь ядер Xe со 128 векторными блоками, два конвейера геометрии и восемь блоков трассировки лучей. Каждое ядро Xe содержит 16 векторных блоков шириной 256 бит и 192 кбайт кэша L1.

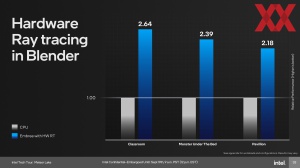

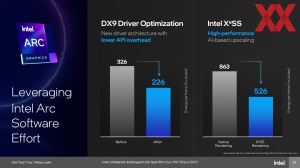

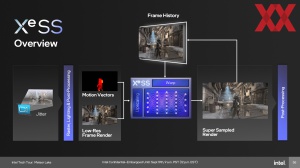

На что способен блок интегрированной графики, мы увидим, когда возьмем в руки первый ноутбук на процессоре Meteor Lake. Доработка драйвера Arc в течение последних двенадцати месяцев, конечно, должно оказать положительное влияние. XeSS также играет важную роль для поддержки производительности, чтобы обеспечить максимально возможную частоту кадров.

Интересно, что Xe-LPG поддерживает вычисления с двойной точностью FP64, которые отсутствовали в архитектуре Xe-HPG на нынешних видеокартах Arc. Значит, Intel и здесь чему-то научилась.

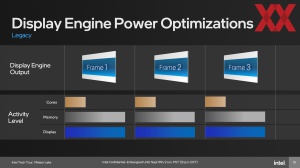

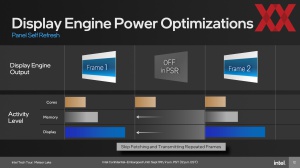

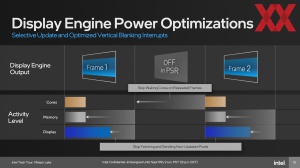

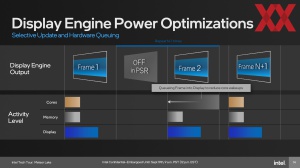

Для повышения эффективности Intel использует две технологии в связке с блоком интегрированной графики. Panel Self Refesh (PSR) не является новой технологией и уже давно применяется. Идея заключается в том, что в обычном режиме на дисплей с частотой обновления, скажем, 60 Гц необходимо подавать 60 новых кадров в секунду, даже если они одинаковые. Для отображения каждого кадра требуется работа ядер, памяти и движка дисплея. Но при обновлении через PSR работа всех этих компонентов не обязательна. Что должно положительно сказаться на времени автономной работы.

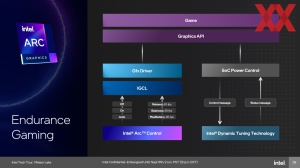

Intel также предлагает новую программную функцию для 3D-рендеринга и игр. Endurance Gaming позволяет задавать определенные цели экономии с помощью Arc Control, одновременно поддерживая целевой показатель FPS.

Быстрые и разнообразные интерконнекты

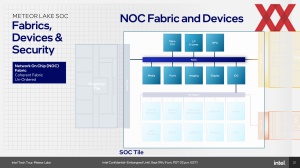

Когда между собой соединяется так много различных IP-блоков и тайлов, выбор правильной технологии интерконнекта имеет решающее значение. Мультимедийный блок, графический тайл, NPU - все эти блоки способствуют увеличению трафика данных и должны быть соединены соответственно быстро.

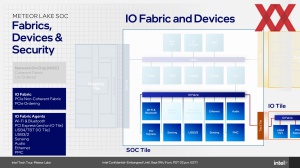

Порт ввода/вывода в тайле SoC, например, является критически важным компонентом, поскольку через него проходят все важные данные. В предыдущей конструкции чипа блок интегрированной графики обращался к кэшу L3/LLC (кэш последнего уровня) Core Complex, который был представлен соответствующей кольцевой остановкой в кольцевом интерконнекте. Теперь графический тайл имеет свой собственный кэш L3, поскольку в противном случае графическому блоку пришлось бы обращаться к LLC Core Complex, и соответствующий трафик данных проходил бы через тайл SoC.

Для связи между тайлом SoC и вычислительным тайлом Intel использует Scalable Fabric на основе интерфейса in-die, который может работать на разных частотах. Максимальная пропускная способность Scalable Fabric находится на уровне подключения внешней памяти, поскольку в конечном итоге данные должны быть переданы от контроллера памяти в SoC-тайле к Core Complex в вычислительном тайле.

Тайл ввода/вывода подключен к тайлу SoC через контроллер ввода/вывода IOC. Между SoC и графическим тайлом используется iCXL, который похож на соединение PCI Express.

Гибкое управление питанием

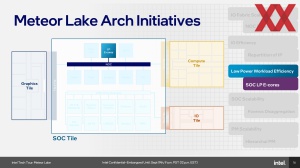

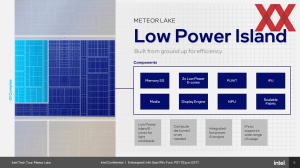

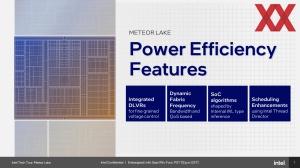

Эффективность включает в себя не только дезинтеграцию отдельных компонентов и перераспределение по тайлам, но и максимально эффективное управление питанием. Каждый тайл содержит контроллер управления питанием PCM (Power Management Controller). Для еще более тонкого управления в тайле SoC имеются дополнительные PMC, которые отвечают за различные блоки тайла SoC. Тайлы ввода/вывода и вычислительный тайл представляют собой так называемые островки низкого энергопотребления (Low Power Islands), которые могут быть полностью отключены для экономии энергии. Теоретически процессор Meteor Lake может работать только через SoC-тайл.

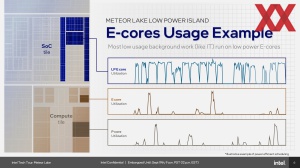

Важная фактор эффективности – ядра LP E, поскольку они будут наиболее часто используемыми ядрами процессора Meteor Lake. На них возлагается вся фоновая обработка. При необходимости к ним подключаются E-ядра на вычислительном тайле. Ядра P включаются только тогда, когда их производительность действительно необходима.

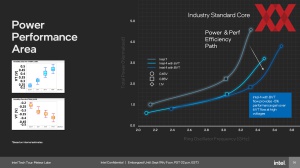

В предыдущих моделях процессоров Intel уже использовались цифровые линейные регуляторы напряжения DLVR (Digital Linear Voltage Regulator) для питания, но не всегда. В Meteor Lake с помощью DLVR можно раздельно управлять ядрами P и E, а также IP-блоками.

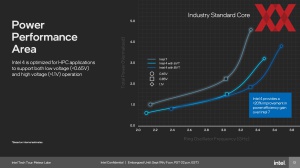

Все эти меры служат для повышения эффективности процессора - поддержания его работы в идеальном рабочем окне для заданной тактовой частоты и необходимого напряжения. Эффективность была одним из важнейших факторов при проектировании Meteor Lake - от дезинтеграции до микроархитектуры ядер.

Производство по техпроцессу Intel 4 – по крайней мере, частично

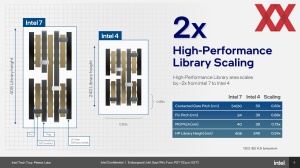

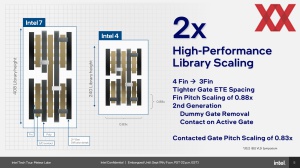

Как уже упоминалось при описании отдельных тайлов Meteor Lake, Intel полагается на новое собственное производство Intel 4 только для вычислительного тайла

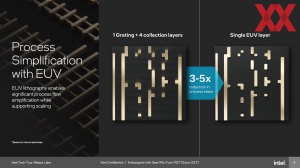

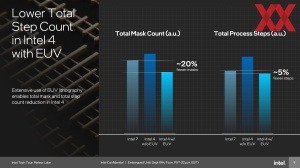

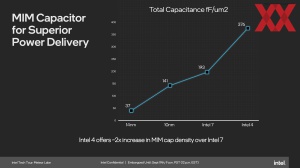

Intel 4 - это первый техпроцесс чипового гиганта, в котором для некоторых этапов экспонирования используется экстремальный ультрафиолет EUV (Extreme Ultraviolet). Использование EUV упрощает некоторые этапы производства и позволяет обходиться меньшим количеством экспозиций. А именно можно сократить три-пять технологических операций.

Слишком сложное взаимодействие некоторых этапов экспонирования и материалов стало причиной длительных задержек с производством по техпроцессу 10 нм, которые Intel преодолела только после переименования в Intel 7. В некоторых случаях для корректного экспонирования металлических слоев M0 и M1 в 10-нм чипах Intel приходилось использовать 20 ступеней и 20 масок. Это, конечно же, требовало больших затрат времени и денег, поэтому было неприемлемо для массового производства. Теперь в Intel 4 все намного проще, в общей сложности требуется на 60% меньше масок, чем в Intel 7.

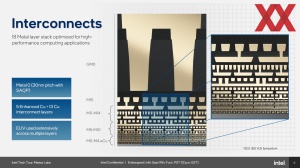

Чип состоит из 18 слоев, из которых в первых пяти используется улучшенная медь. Для Intel 7 применялись медные слои и чистый кобальт. Шаг в верхнем металлическом слое (M0) составляет 30 нм.

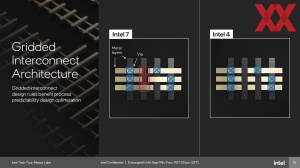

Для упрощения проектирования металлических слоев и всего чипа Intel установила новые правила. В частности, ограничены области, в которых возможно применение сквозных линий TSV. Таким образом, области без TSV могут быть лучше оптимизированы, а производство упрощено.

С Intel 4 чиповый гигант говорит о лучшем выходе годных кристаллов для нового техпроцесса за последние 10 лет - примерно на том же уровне, который сегодня дает оптимизированный 10-нм техпроцесс. Intel 3 будет опираться на Intel 4 и обеспечит большую гибкость кривой VF. Таким образом, Intel 3 - это не совсем новая производственная ступень, а промежуточный этап, подобно тому, как Intel 18A будет сочетаться с Intel 20A.

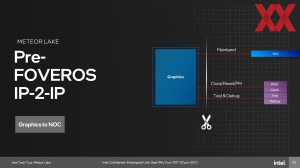

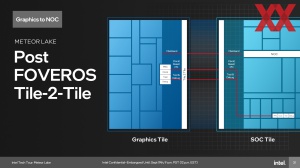

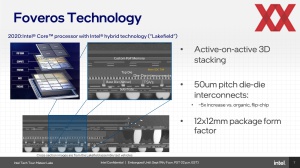

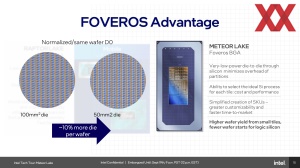

Foveros в корпусировке

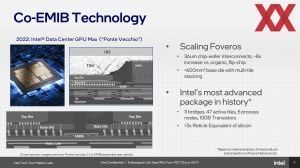

Для Meteor Lake используется корпусировка Foveros. После Lakefield (тест) и Ponte Vecchio, Meteor Lake - это первый случай использования Foveros в массовых чипах, производящихся в больших количествах.

Разработка Foveros началась около шести лет назад. Мы протестировали Lakefield уже в середине 2020 года, причем там использовался Foveros. Этот факт показывает, что технологии корпусировки были разработаны довольно давно, но Intel еще не так далеко продвинулась в других областях (предположительно, в производстве самих кристаллов).

Однако для Meteor Lake используется уже не первая итерация Foveros с шагом между шариковыми контактами 50 мкм, а усовершенствованная версия с шагом 36 мкм.

С физической точки зрения все соединения Tile-2-Tile идентичны. В кристалле Foveros имеются тысячи соединений, которые можно использовать с различными протоколами. Как раз разные протоколы и тактовые частоты приводят к разной пропускной способности соединений Tile-2-Tile. Однако задержки всегда одинаковы, поскольку отсутствуют или почти отсутствуют накладные расходы на протокол, и расстояния также одинаковы.

Для Meteor Lake также следует различать корпусировку Foveros (Foveros Complex), которая содержит пять тайлов, соединенных друг с другом через Foveros, и собственно корпусировку процессора, которая затем размещается на материнской плате в ноутбуке или припаивается к ней. В подложке корпусировки процессора Intel использует интерконнект OPI (On-Package Interconnect). Однако здесь мы сосредоточимся на прямых соединениях Tile-2-Tile.

В тайле SoC имеется интерконнект NOC (Network on a Chip Fabric), который соединяет LP E-ядра, контроллер памяти, NPU, IPU, медиадвижок и движок дисплеев. NOC является кэш-когерентным интерконнектом, то есть кэш доступен всем IP-блокам, подключенным через интерконнект. Остальные блоки соединяет интерконнект ввода/вывода IO Fabric. NOC и IO Fabric соединяются между собой с помощью контроллера ввода/вывода IOC.

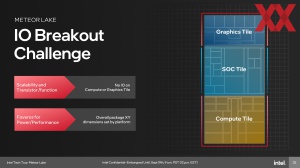

При проектировании корпусировки необходимо было учитывать, что соединения ввода/вывода (так называемые I/O breakouts) возможны только на тайлах SoC и I/O. Графический и вычислительный тайлы не имеют внешних соединений. Соответственно, размеры SoC и, прежде всего, тайла ввода/вывода были спланированы таким образом, чтобы для соединений ввода/вывода оставалось достаточно места.

Но корпусировка также имеет и другие проблемы, поскольку в основном производство чипов как таковых упрощается, но корпусировка становится гораздо более сложной. Таким образом, мы наблюдаем смещение сложности от кристаллов к корпусировке.

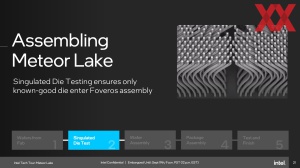

На этапе Singulated Dire Test каждый чип проверяется перед тем, как его помещают в корпусировку. Конечно, стоит избегать установки в корпусировку дефектных кристаллов: если это обнаружится только потом, то вся корпусировка будет непригодна для использования. Необходимо выявить и отсортировать как можно больше дефектных чипов, поскольку при наличии пяти кристаллов в корпусировке доля выхода годных чипов будет пропорционально ухудшаться.

Следующий шаг – сборка корпусировки Foveros Complex. Кристаллы Foveros Complex размещаются на подложке. Затем проводится тестирование Foveros Complex. Здесь мы хотели бы дать ссылку на наш отчет о посещении завода корпусировки Intel в Малайзии, поскольку он дает некоторое представление о сложном тестировании и корпусировке чипов.

Для первых тестовых чипов Meteor Lake корпусировка Foveros пока осуществляется в Орегоне (США). Для массового производства будет использоваться завод в Аризоне и завод в штате Нью-Мексико. Но Intel хочет продавать Meteor Lake и последующие поколения миллионами единиц, а для этого нужны гораздо большие мощности. Например, к 2025 году они должны увеличиться в четыре раза.

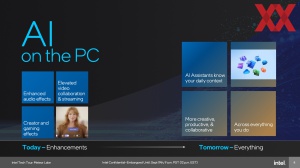

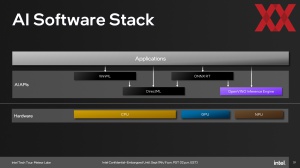

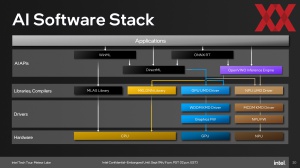

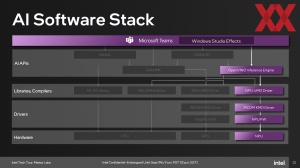

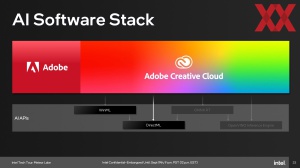

Meteor Lake и искусственный интеллект

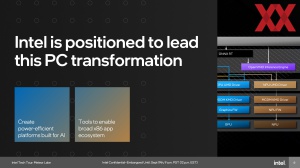

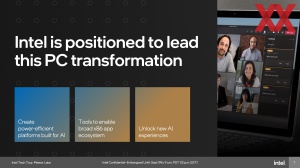

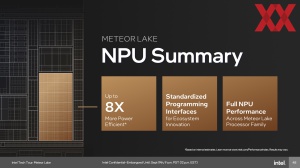

Практически все производители - будь то Intel, AMD или NVIDIA - видят необходимость в специализированных ускорителях для ИИ. Хотя в некоторых сегментах искусственный интеллект уже давно используется (см. DLSS от NVIDIA или ПО для анализа изображений), в ближайшие годы ожидается значительный рост требований по вычислениям ИИ.

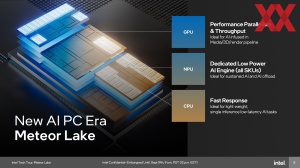

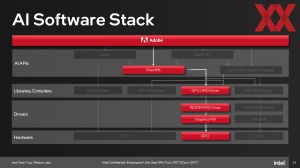

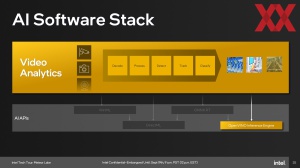

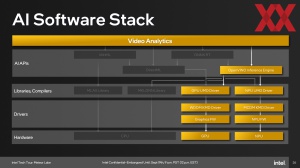

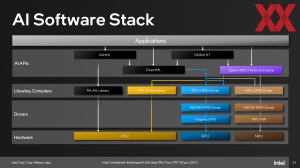

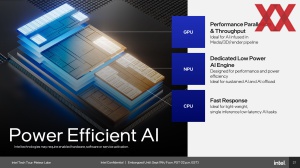

В будущем рабочие нагрузки ИИ смогут использовать сразу три «ускорителя» или ресурса. GPU по-прежнему будет способен выполнять рабочие нагрузки ИИ в распараллеленном виде и достигать высокой пропускной способности. Это идеально подходит для фото-, видео- и 3D-контента, генерируемого или обрабатываемого с помощью искусственного интеллекта.

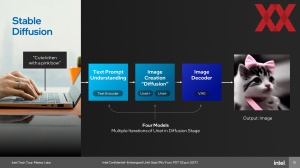

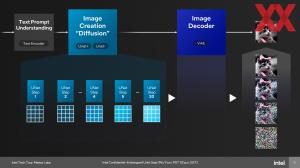

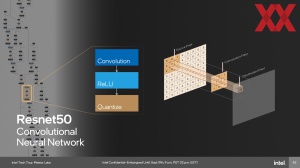

Ядра CPU также могут выполнять легкие задачи инференса. А интегрированный NPU берет на себя задачи ИИ, которые выполняются постоянно или являются значительно более сложными. К ним относятся обнаружение потоков (Thread Detection), а также выделение другого фона в веб-конференции или подавление шума.

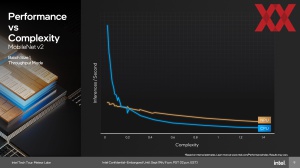

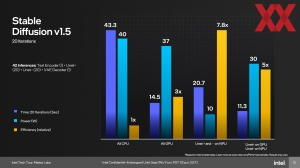

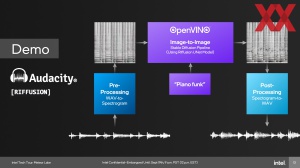

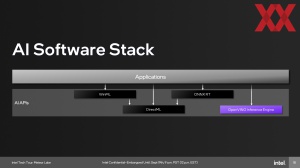

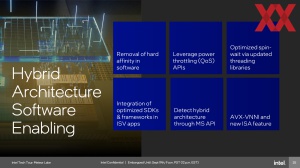

От конкретного приложения зависит, какие ускорители будут работать быстрее или эффективнее. На примере Stable Diffusion видно, что GPU справляются быстрее, но требуют большего энергопотребления. На NPU обработка не такая быстрая, но гораздо более эффективная. Теоретически приложения могут получить доступ ко всем ресурсам-ускорителями. Однако в Meteor Lake это еще не так. Разработчики программного обеспечения могут получить доступ к аппаратному обеспечению через ONNX, OpenVINO, W3C и DirectML в качестве интерфейса или фреймворка. Программное обеспечение Adobe, Zoom, Blackmagic, Avid и многих других компаний сможет использовать аппаратные ускорители ИИ. Но распределение аппаратных средств фиксировано, динамическое переключение с GPU на NPU не предусмотрено.

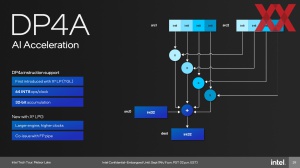

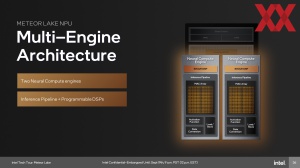

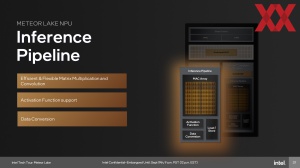

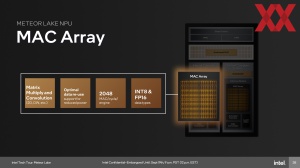

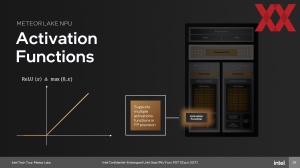

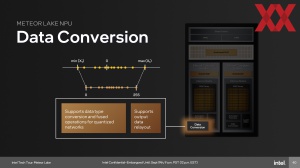

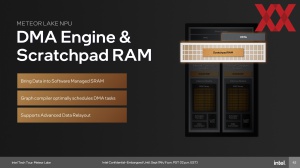

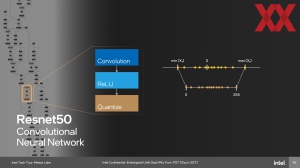

В Meteor Lake используется IPU NPU третьего поколения. NPU содержит память Scratchpad SRAM, которая используется для хранения данных, обрабатываемых в NPU. NPU когерентен по кэшу с системной памятью. Вычисления производятся двумя кластерами массивов MAC (Neural Compute Engines), которые представляют собой простые матричные блоки, как мы уже знаем по блокам MXM архитектуры Xe.

Вычислительная производительность составляет 2.048 MAC (операций умножения-сложения) за тактовый цикл на один движок при использовании INT8. При двойной точности (FP16) она по-прежнему составляет 1.024 MAC за такт.

Два нейронных движка могут работать как над одной задачей, так и разделяться между двумя, в зависимости от того, какие приложения выполняются и каковы требования.

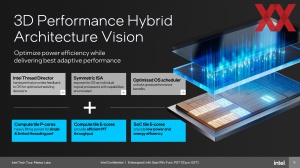

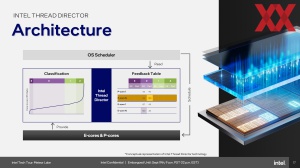

3D Performance Hybrid Architecture и проблемы

Гибридная архитектура, представленная с процессорами Alder Lake за счет использования ядер E и P, поначалу вызвала много опасений. Пользователи сомневались, сможет ли операционная система справиться с разными классами ядер. Действительно, на начальном этапе возникло несколько проблем, особенно с играми, которые работали на ядрах E, а не P, но планирование с помощью Thread Director и соответствующая интеграция в Windows в итоге оказались лучше, чем ожидалось.

В процессорах Meteor Lake компания Intel представляет еще один класс ядер E. Ядра LP E предназначены для выполнения всех фоновых задач, и поэтому они наверняка будут чаще всего использоваться. Классические ядра E отвечают за многопоточную производительность с максимально возможной эффективностью. Ядра P включаются при запуске интенсивных вычислительных задач.

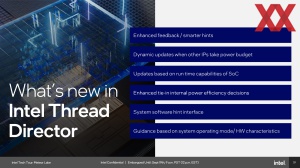

Thread Director будет адаптирован для новых ядер LP E. Прежняя процедура предусматривала, в частности, периодическое переключение потоков с ядер E на ядра P с целью их повторной классификации. Теперь же с процессорами Meteor Lake Thread Director будет пытаться удержать потоки на ядрах LP E тайла SoC. Если это невозможно, то поток перемещается на ядра E вычислительного тайла. Однако это не совсем тривиальный процесс, поскольку необходимо также обмениваться данными в кэшах. Такой процесс перемещения сравнительно накладный, по возможности его следует избегать.

Первые ноутбуки на рубеже года

На этом наш теоретический экскурс в архитектуру процессоров Meteor Lake заканчивается. Из собственных источников и заявлений Intel мы уже знаем, что процессоры Meteor Lake будут выпускаться в разных конфигурациях. Вычислительный тайл будет доступен с 6P+8E ядрами и с 2P+4E ядрами. Для графического тайла также планируется две конфигурации с четырьмя и восемью ядрами Xe. Intel уже упоминала, что возможны два варианта тайла ввода/вывода. Однако пока неизвестно, в каких комбинациях процессоры Meteor Lake в конечном итоге будут выпущены на рынок.

Intel потратила целый день на то, чтобы раскрыть прессе подробности Meteor Lake. В том числе было рассказано о совместной работе с партнерами по ноутбукам над новыми концепциями охлаждения и т.п. В каждом из аспектов, которые мы рассмотрели в этой статье, чувствуется стремление создать максимально эффективный процессор. Остается только ждать практических результатов и тестов. От того, как быстро программное обеспечение сможет использовать ускорители искусственного интеллекта в виде NPU и VPU, будет зависеть и практическая отдача.

Сегодня мы пока не можем назвать конкретные модели процессоров Meteor Lake, но, по крайней мере, знаем официальную дату запуска. Процессоры будут анонсированы 14 декабря, но неясно, увидим ли мы уже тогда первые ноутбуки с Meteor Lake в магазинах. Скорее всего, придется дождаться начала следующего года. Поэтому стартовой площадкой вполне может стать выставка CES в Лас-Вегасе в начале января.