Наряду с переносом первой реализации Back Side Power Delivery Network (BSPDN) на техпроцесс A16, компания TSMC объявила на Technology Symposium 2024 о значительных улучшениях запланированных этапов производства N2, которые должны существенно повысить эффективность. В том числе упоминается технология NanoFlex, как сообщает Anandtech.

Наряду с переносом первой реализации Back Side Power Delivery Network (BSPDN) на техпроцесс A16, компания TSMC объявила на Technology Symposium 2024 о значительных улучшениях запланированных этапов производства N2, которые должны существенно повысить эффективность. В том числе упоминается технология NanoFlex, как сообщает Anandtech.

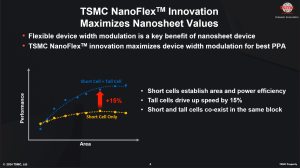

Все ранее запланированные этапы техпроцесса N2 (N2, N2P, N2X) будут поддерживать NanoFlex. Это технология упрощает использование различных библиотек ячеек и транзисторов. Напомним, что для области логики процессора используются другие библиотеки, чем для кэша. Некоторые области должны обеспечивать более высокую тактовую частоту, в то время как другие необходимо максимально плотно упаковать.

Поскольку все этапы техпроцесса N2 будут опираться на новые нанолистовые транзисторы, TSMC усовершенствовала технологию FinFlex, чтобы она поддерживала NanoFlex для новых транзисторов. В зависимости от функциональной области, технология NanoFlex сделает чипы на 15% быстрее или обеспечит большую эффективность.

Тестовое производство N2 запланировано на 2025 год. TSMC ожидает, что массовое производство начнется во второй половине года. Первые устройства, оснащенные чипами на новом техпроцессе, можно ожидать с 2026 года. Вскоре после этого можно ожидать появление варианта N2P с повышенной производительностью и варианта N2X, оптимизированного по напряжению. За N2P последует техпроцесс A16, в котором впервые будет использована подача питания сзади кристалла через Super Power Rail (SPR).

Как уже упоминалось, в N2 впервые будут использованы нанолистовые транзисторы. Чтобы обеспечить более качественное и стабильное питание транзисторов, TSMC использует конденсаторы SHPMIM (Super-High-Performance Metal-Insulator-Metal), которые встраиваются в слой подачи питания. В Intel аналогичные компоненты называются Super Metal Insulator Metal (MIM). По сравнению с конденсаторами SHDMIM (Super-High-Density Metal-Insulator-Metal), которые в настоящее время используются в TSMC, новые конденсаторы SHPMIM имеют вдвое большую емкость при меньшем сопротивлении.

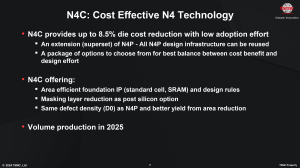

Экономически эффективный техпроцесс N4C запланирован на 2025 год

TSMC также объявила о разработке недорогого техпроцесса N4C к 2025 году. Как и все другие этапы N4, он основан на техпроцессе 5 нм. TSMC для N4C создала новый дизайн для стандартных ячеек и ячеек SRAM, что позволило снизить стоимость производства пластины N4C на 8,5%. Еще одним фактором является уменьшение числа слоев маски. Подобное снижение себестоимости наверняка ощутят на себе и заказчики.

Чипы, которые в настоящее время производятся по техпроцессу N4P, можно легко перевести на N4C. TSMC говорит о более высокой доле выхода годных кристаллов из-за уменьшения площади и такой же плотности дефектов (D0), как и при использовании техпроцесса N4P. Кроме того, заказчики могут перейти сразу на N4C, не имея в своем распоряжении чипов, ранее изготовленных на N4P. Массовое производство первых чипов по техпроцессу N4C планируется начать в 2025 году.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).