Как сообщают коллеги Anandtech, компания TSMC на Technology Symposium 2024 в Санта-Кларе представила обновленные производственные планы. Несмотря на свое нынешнее превосходство в области экспонирования и корпусировки пластин (особенно по объему заказов), TSMC традиционно проявляет осторожность, когда речь заходит о новых техпроцессах и технологиях.

Как сообщают коллеги Anandtech, компания TSMC на Technology Symposium 2024 в Санта-Кларе представила обновленные производственные планы. Несмотря на свое нынешнее превосходство в области экспонирования и корпусировки пластин (особенно по объему заказов), TSMC традиционно проявляет осторожность, когда речь заходит о новых техпроцессах и технологиях.

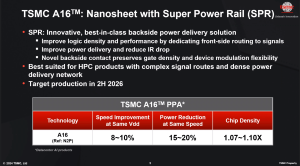

Впервые TSMC официально указала первый техпроцесс эры Ангстрема: A16. A14 и A10 уже упоминались несколько месяцев назад в прогнозе по масштабированию техпроцессов. Ожидается, что первые чипы A16 сойдут с конвейера во второй половине 2026 года. По сравнению с техпроцессом N2P, который еще не запущен в производство, A16 обеспечит повышение производительности на 8-10 % при том же энергопотреблении. И наоборот, при той же производительности возможно снижение энергопотребления на 15-20 %. Что касается плотности транзисторов, то она увеличится в 1,07-1,1 раза.

A16 станет первым техпроцессом TSMC, в котором будут использоваться как нанолистовые транзисторы, так и Super Power Rail (SPR). SPR – это подача питания с обратной стороны кристалла (Back Side Power Delivery Network, BSPDN), аналогичная PowerVia от Intel. Однако существуют различные варианты реализации BSPDN.

Изначально использование Super Power Rail планировалось еще в техпроцессе N2P. Теперь TSMC переносит технологию на A16. Причины не раскрываются.

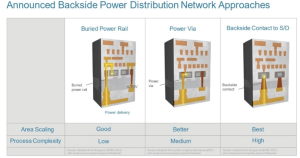

По уровню реализации и технической сложности SPR от TSMC находится на одном уровне с PowerVia от Intel. Первая реализация Buried Power Rail предусматривала подачу питания с задней стороны подложки, затем линии питания логических ячеек подключались через nano TSV. Такой подход обеспечивал некоторое масштабирование, не слишком сильно усложняя производство. Вторая реализация Intel PowerVia предусматривает подачу питания уже на контакт ячейки или транзистора, что дает лучший результат, но повышает сложность.

Техпроцесс TSMC A16 предназначено для продуктов HPC. По всей видимости, это все еще самый большой растущий рынок производства современных чипов. Судя по графикам TSMC и Intel, соответствующим аналогом станет Intel 14A. Для Intel 14A чиповый гигант тоже будет использовать PowerVia. Intel также планирует перейти на High-NA EUV для этого техпроцесса.

На симпозиуме ожидаются дополнительные подробности. В частности, речь пойдет о корпусировке, которая представляет собой вторую серьезную технологическую проблему наряду с собственно экспонированием пластин.

Обновление:

Появилась дополнительная информация о том, что Super Power Rail (SPR) от TSMC идет на шаг дальше в плане интеграции, чем PowerVia от Intel.

Хотя PowerVia подключает питание через вертикальные Nano TSV, необходимо также интегрировать горизонтальный уровень подключения. BSPDN to S/D, или, как его называет TSMC, SPR, подводит питание непосредственно к истоку и стоку транзистора. Это позволяет сэкономить еще больше места, но значительно усложняет производство. Ожидается, что в таком виде Intel реализует второе поколение PowerVia.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).