Вот уже около десяти лет названия технологических процессов все дальше и дальше расходятся с реальными размерами. То, что TSMC называет N3 или Intel называет Intel 7, не имеет прямой связи с размерами производимых транзисторов. Intel решила изменить названия техпроцесса в середине 2021 года, чтобы вновь встать на один уровень с конкурентами, по крайней мере, в плане наименования.

Вот уже около десяти лет названия технологических процессов все дальше и дальше расходятся с реальными размерами. То, что TSMC называет N3 или Intel называет Intel 7, не имеет прямой связи с размерами производимых транзисторов. Intel решила изменить названия техпроцесса в середине 2021 года, чтобы вновь встать на один уровень с конкурентами, по крайней мере, в плане наименования.

Теперь Samsung, по всей видимости, также планирует изменить название техпроцесса, чтобы выглядеть более конкурентоспособной. Об этом сообщает ZDNET Korea. Второе поколение 3 нм техпроцесса (SF3) будет переименовано в 2 нм при массовом производстве. Неизвестно, коснется ли это и SF3P (см. планы) и будут ли запланированные процессы SF2 и SF2P переименованы в следующий технологический этап SF1.4.

По данным ZDNET Korea, Samsung уже проинформировала своих клиентов о переименовании. Сообщается, что названия техпроцессов уже изменены в контрактах.

Samsung не в первый раз поступает подобным образом. В середине 2020 года Samsung переименовала второе поколение своего 7-нм техпроцесса в 5-нм. В данном случае компания также хотела учесть улучшенную производительность.

Samsung пока не давала официальных комментариев по этому поводу. Массовое производство по переименованному в 2 нм техпроцессу Samsung планирует начать во второй половине 2024 года. Хотя южнокорейская компания по-прежнему является вторым по величине контрактным производителем полупроводников, заявление Intel о том, что она теперь хочет конкурировать на этом рынке, вероятно, окажет давление на Samsung.

Присмотримся к характеристикам

Размеры отдельных транзисторов больше не имеют ничего общего с названиями технологических процессов. Мы можем подробнее рассмотреть это на примере:

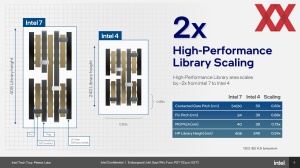

Intel недавно сделала несколько заявлений о размерах ячеек своей так называемой высокопроизводительной библиотеки High Performance Library для техпроцессов Intel 7 и Intel 4. Указана высота ячейки, а также масштабирование. В функциональной ячейке находится не один транзистор, а несколько, что связано с повышением производительности и тактовой частоты.

Шаг ребер Fin Pitch, то есть расстояние между ними, уменьшен с 34 до 30 нм. Шаг затворов Gate Pitch - с 54/60 до 50 нм. Ни в одном из транзисторных элементов мы не находим 7 или 4 нм. Названия техпроцессов давно перестали иметь что-то общее с действительностью. Кроме того, каждый производитель полупроводников может вносить определенные коррективы в техпроцесс для своих клиентов (или Intel для собственных продуктов). Такие коррективы вносят AMD и NVIDIA для своих техпроцессов на TSMC, а также как Intel для своих клиентов Foundry для техпроцессов Intel 3 или Intel 18A.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).